一家集研发、生产和销售为一体的高新技术企业

20年专业经验 前沿技术研发新产品

芯派科技咨询热线:

20年专业经验 前沿技术研发新产品

芯派科技咨询热线:

最近一系列事件再次表明,制约中国芯片产业发展的主要因素已集中到制造能力。如何快速提升制造能力,推动芯片产业发展?只有不断地研发和创新。

在芯片界,摩尔定律一直占据统治地位。摩尔定律接下来是终结还是延续,已成为过去十年芯片界热议的话题。摩尔定律自1965年发明以来,一直引领着世界半导体产业向实现更低的成本、更强的性能、更高的经济效益的目标前进。然而,随着半导体技术逐渐逼近硅工艺尺寸极限,原摩尔定律导出的“IC的集成度约每隔18个月翻一倍,而性能也将提升一倍”的规律将受到挑战。

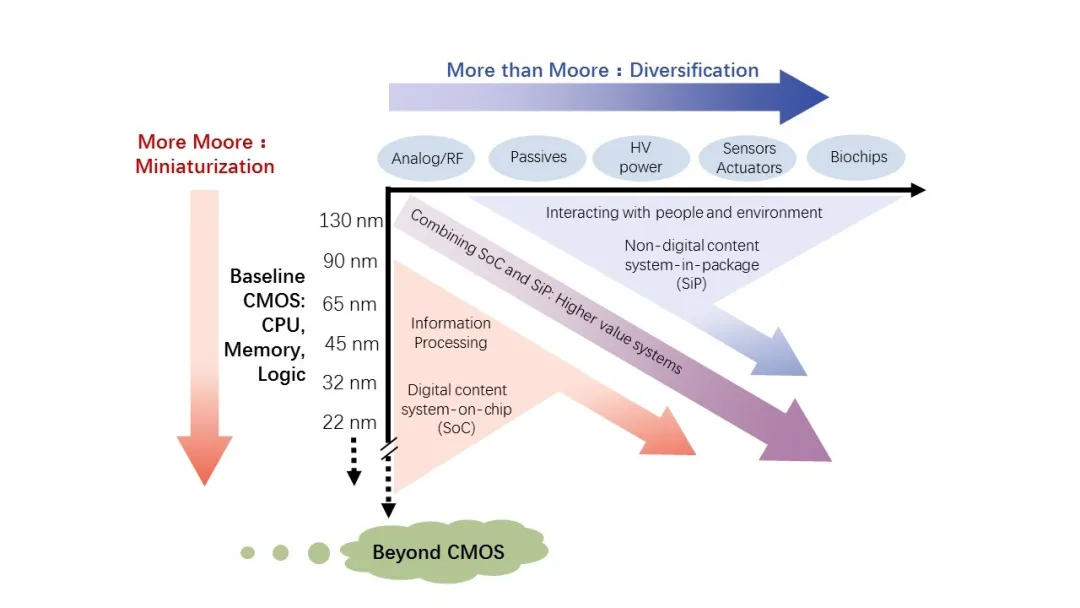

半导体制造工艺的两种演进路线图

为此, ITRS组织针对半导体产业中远期发展的挑战,在技术路线制定上,提出选择两种发展方式(如图1):一是继续沿着摩尔定律按比例缩小的方向前进,专注于硅基CMOS技术;二是按“后摩尔定律”的多重技术创新应用向前发展,即在产品多功能化(功耗、带宽等)需求下,将硅基CMOS和非硅基等技术相结合,以提供完整的解决方案来应对和满足层出不穷的新市场发展。

· 继续使用先进节点,迈向5纳米及以下

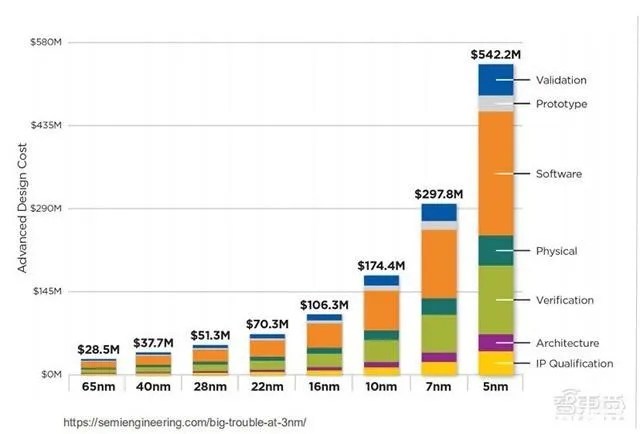

使用先进节点的好处很多,晶体管密度更大、占用空间更少、性能更高、功率更低,但挑战也越来越难以克服。极小尺寸下,芯片物理瓶颈越来越难以克服。尤其在近几年,先进节点走向10nm、7nm、5nm,问题就不再只是物理障碍了,节点越进化,微缩成本越高,能担负巨额研发费用并实现盈利的设计公司越来越少。

· 以“三维集成”延续摩尔定律

幸运的是,每当摩尔定律被唱衰将走到尽头,总会激发出科学家和工程师们创新构想,提出力挽狂澜的突破性技术,将看似走向终结的摩尔定律以“后摩尔定律”的形式延续下去。“后摩尔定律”的实质是,它除了会延续摩尔定律对集成度、性能的追求外,还会利用更多的技术,例如模拟/射频、高压功率电源、MEMS传感器、生物芯片技术及系统级封装(SiP)等三维集成技术,以提供具有更高附加值的系统。

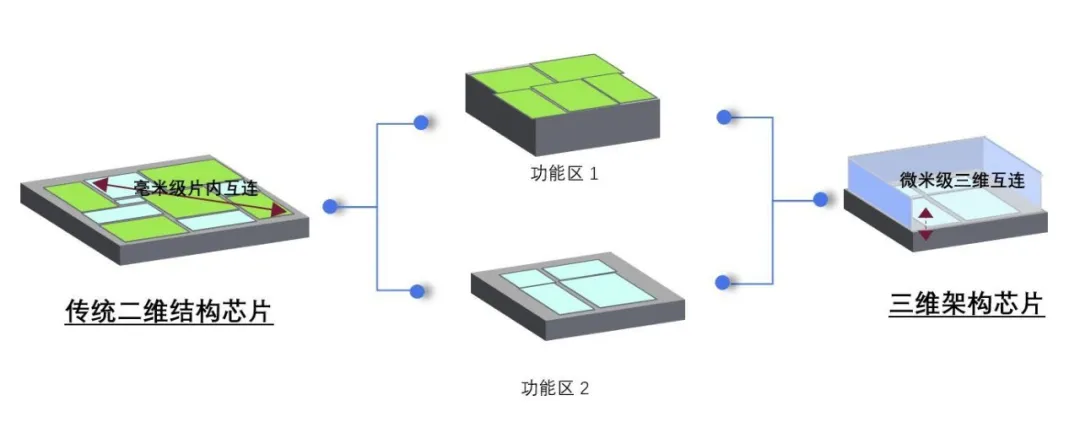

ITRS指出,在“后摩尔定律”范畴,随着新兴应用不断出现,智能化微系统芯片将会进入三维集成时代。三维集成技术概览和两条主要的工艺路线

三维集成电路又称立体集成电路,是集成电路从传统平面集成方式向垂直方向立体集成方式延伸的产物。三维集成电路的优势在于:多层器件重叠结构使芯片集成度成倍提高;TSV和混合键合工艺使芯片间互连长度大幅度缩短,提高传输速度并降低了功耗;多种工艺混合集成,使集成电路功能多样化;减少封装尺寸,降低设计和制造成本。三维集成技术可将多层集成电路芯片或晶圆堆叠键合,通过三维互连实现多层之间的电信号连接。三维集成技术能实现异质芯片互连结合,发挥出最高系统性能水平,是其独特的最大优势。

· 晶圆间三维堆叠技术

通过键合堆叠和连通孔工艺的持续改进满足芯片对更大带宽、更小功耗的要求。其工艺目前主要用于图像传感器的生产,近些年,随着物联网、人工智能和5G对更大带宽、更小功耗和更低延时等特性产品的要求,晶圆级三维集成开始应用于大容量存储、存算一体、高性能计算等领域。代表厂家有Intel、TSMC、Samsung、SONY等。

· 多颗芯片间三维互连技术

芯片级三维集成,主要追求芯片间凸点(Bump)连接小型化,来提高集成度和芯片性能。其技术特点依托于封装打线(Wire bond)和凸点(bump)为基础,把不同功能的芯片通过毫米级的封装工艺连接。代表厂家主要为半导体制造领域的后端封装厂,如Amkor、SPIL、ASE、长电、华进等。

二者互有优劣,晶圆间堆叠工艺精度高、互联密度大;但相较芯片间互连,其良率相对较低、对芯片尺寸匹配度要求高。